行泊一体尚在量产前夜,舱泊融合仍在发力,跨域融合的下个技术热点——舱驾一体已经在路上了。可见,汽车电子的迭代周期似乎正追随摩尔定律,迅速而彻底。

舱驾一体显露头角,上车提速

当行业都在大谈行泊一体、舱泊融合的时候,舱驾一体的话题热度同样居高不下。比如在2023上海车展上,纵目科技与博泰车联网联合宣布,双方将在智能汽车领域展开深度合作,基于行业现下主流芯片平台共同打造具有高性价比且能够覆盖主流场景,并快速落地的高市场接受度的“舱驾一体”的系统解决方案。据了解,该解决方案整体可减少超30%的成本支出。

又如斑马智行与禾多科技战略合作,推进“智能驾驶OS+自动驾驶AI”深度融合,探索在OS底层推进智能驾驶域和智能座舱域一体化联通,加速舱驾一体智能驾驶方案落地。目前,双方已通过AliOS初步搭建起“智能座舱+智能驾驶”共创平台。

中科创达高级副总裁、智能汽车事业群总裁常衡生更是直言,“舱驾一体”已经成为行业趋势,中科创达正在开发相关解决方案,相关方案预计在今年第三季度发布。

而沿着车展所绽放的一隅风景往回看,其实业内不少企业早已经搭建起了庞大的舱驾融合的技术“拼图”。尤其是自2022年开始,舱驾融合方案不断被提及,有如“雨后春笋”般破土而出。

2022年8月,在世界新能源汽车大会WNEVC 2022期间,百度IDG智驾融通创新部总经理苏坦坦言,舱驾融合已经具备技术性基础,功能融合已经开始出现,换句话说,舱驾融合已经到了向前突破的时间点。百度推出的下一代智能座舱软硬一体的产品Apollo Robo-Cabin(采用高通8295芯片),便体现了“舱-驾-图”三方合力。目前,百度正在不断解码舱驾融合新赛道。

同年11月,芯驰与斑马智行联合宣布,将基于AliOS Cyber和智能座舱芯片“舱之芯”X9系列深度合作,率先共建行业首个全栈式舱行泊一体方案,使座舱、行车和泊车场景共用一套芯片、传感器和域控制器,加速推进座舱和智驾系统的融合,预计2024年实现量产落地。

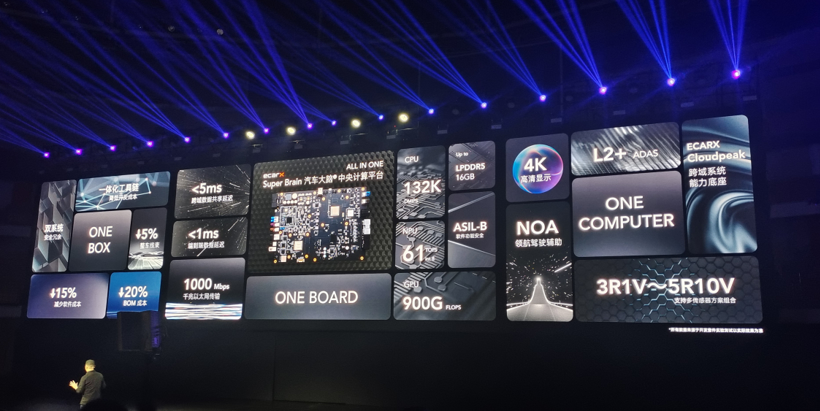

今年3月,亿咖通推出的中央计算平台Super Brain,基于龍鷹一号和黑芝麻智能A1000智能驾驶芯片打造,同样致力于舱驾一体解决方案。

亿咖通Super Brain;图片来源:盖世汽车

跨域融合进阶,舱驾一体待势乘时

汽车的智能化程度取决于底层的EE架构,针对分布式架构迈向中央集中式架构的大趋势,业界的主要思路便是先将部分域的功能集成到一个高性能计算单元内,即在功能域控制器内集成;再逐渐聚合更多的功能域,进一步跨域融合;最终实现1个中央计算大脑。

近两年大火的行泊一体、舱泊一体以及舱驾融合,均是整车电子电气架构演进过程中的一个阶段性产物。

在传统分布式架构阶段,行车和泊车两大系统分别有各自的传感器和控制器。这种架构下,当一套系统启用时,另一套系统就会闲置,由此造成了严重的资源浪费,也无法形成真正的数据闭环。

于是,过去两年业界纷纷开始探索将行车和泊车功能在一个域控制器上集成,行泊一体方案应运而生。

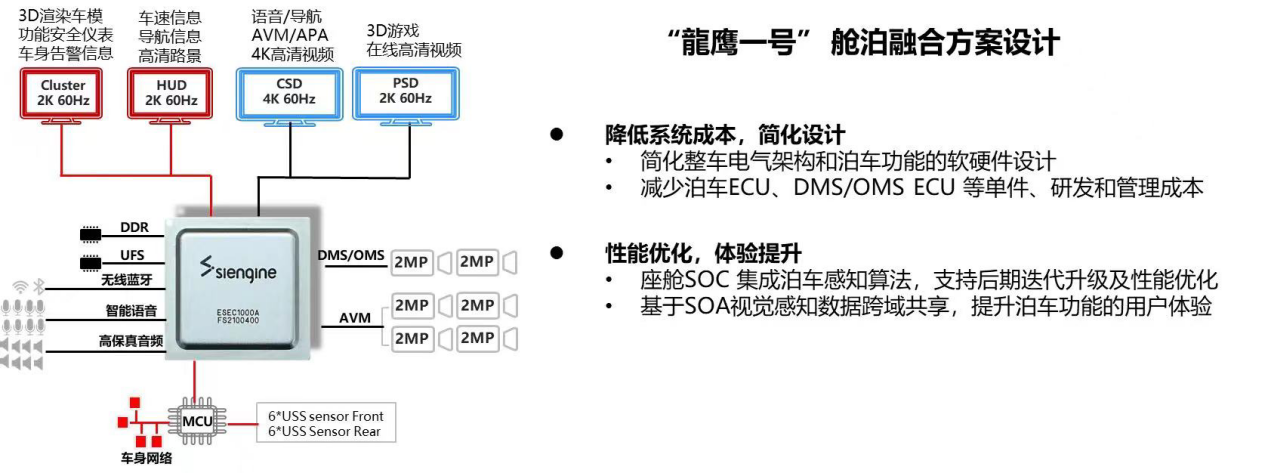

而随着电子电气架构继续向跨域融合演进,智能座舱芯片算力同步提升,从座舱域向泊车兼容——舱泊一体方案逐渐成为另一种趋势。

图源:芯擎科技

再进一步,舱驾融合可以说是真正的跨域融合,也是电子电气架构进一步向中央集成式迈进的关键一步,同时也符合降本增效的行业趋势。

所谓舱驾一体,就是将座舱域和智驾域集成到一个高性能计算单元中,同时支持智能驾驶和智能座舱功能,相较于行泊一体和舱泊一体,这种架构的集成度更高,当然对硬件的要求也随之升高。

博泰车联网创始人、CEO应宜伦就表示,域控架构的加速量产,主流高算力计算平台的应用,正在引发新一轮智能网联市场竞争的升级,“舱驾一体”的实现有赖于高算力芯片计算平台。

目前,主流芯片企业也都在积极开发面向跨域融合甚至下一代中央计算架构的高算力芯片。

2022年9月,NVIDIA重磅发布大算力芯片Drive Thor,支持多计算域隔离,同样可实现座舱域、驾驶域融合,支持将辅助驾驶、自动泊车、信息娱乐、DMS等多种功能整合在同一块芯片中运行。CES 2023科技展会上,NVIDIA更是明确2025年量产的Thor芯片支持完整的“舱驾一体”。

2023年1月,全新的骁龙Ride Flex系统级芯片和新的自动驾驶平台(Snapdragon Ride)推出,Ride Flex建立在高通的数字化驾驶舱和高级驾驶辅助平台之上,有助于在相同的硬件上处理工作负载,并且系统级芯片集成骁龙Ride Vision硬件。

图源:高通中国

NVIDIA的Drive Thor和高通Snapdragon Rideflex的GPU算力均超过2000 TOPS,直接在行业内“卷”出新高度。

在国内,黑芝麻智能也于今年4月7日发布行业首个智能汽车跨域计算平台武当系列及其首款芯片C1200,展现出了面向跨域计算场景的实力。据悉,该平台覆盖座舱、智驾、网关等不同领域,具有多种融合功能,瞄准L2+级别智能驾驶及融合计算应用市场。

不过,目前距离舱驾一体芯片真正落地还有一段时间。据了解,NVIDIA Drive Thor预计2025年量产,黑芝麻智能C1200则在今年下半年提供样片,最快也要到明年底量产。

德赛西威于NVIDIA DRIVE Orin SoC运行的舱驾融合产品演示;图源:NVIDIA

上车仍面临诸多挑战

每一个新兴技术的出现,从概念到真正上车,中间往往需要很长时间,舱驾一体亦不例外。

从技术路径来看,目前舱驾一体主要采用的是多SoC芯片集成,如德赛西威的车载计算平台“Aurora”、亿咖通Super Brain等。业界普遍认为,舱驾一体化的最终彼岸,是实现单SoC层面的一体化,这样不仅能够简化设计、降低成本,同时可以做到芯片算力共享。

图源:盖世汽车

然而,融合需要遵守功能安全级别接近或可靠性接近等基本原则,受限于当前的软硬件技术水平、架构方案、以及跨部门协作等因素,舱驾一体在单SoC层面融合的实现,仍需时日。

事实上,高性能的舱驾一体不仅会大幅提升软件的复杂度,也对主控SoC的算力需求、功能安全等提出更高要求。

芯擎科技副总裁兼产品规划部总经理蒋汉平便指出,要在工艺、功耗和成本等受限的情况下尽可能发挥芯片算力;有机融合芯片的各个计算单元算力,加速整个系统的上市时间周期;并做到芯片架构的最优化、效率最高等,这些挑战都不容小觑。所以现阶段主要是在系统侧做融合,最终会从系统层过渡到SoC层。

博世中国首席客户解决方案专家万昕也直言,如何高效地把座舱软件和智驾软件集合在一起,如何应对当前芯片多样化、算力、功能安全、芯片供应的不确定性等问题,是当前主要的考量。这些问题,导致现阶段尚无法用一颗SOC把舱、驾、泊集中在一块,也无法全部支持高阶驾驶功能。因此公司目前采用了先舱泊,再舱驾的路径。

需注意的是,站在整个供应链的角度,在汽车进入智能终端的身份变革中,无论是终端主机厂、科技企业,还是上游Tier1、芯片公司,整个产业链环节都在经历着前所未有的角色转型。跨域融合,迈向舱驾一体、中央集成的终局赛点,无疑在加速这一巨变。

那么,在诸多挑战面前,舱驾一体的大趋势会如何影响供应链各个环节的角色地位?

首先,由于车用芯片特别是高性能处理器占据当前汽车电子的核心部分,它决定着整个汽车的性能和质量,芯片公司因此凭借深耕多年的技术优势,不仅能利用自研芯片的方式降低产品成本,还能基于良好的开发生态与AI算法形成协同效应,并提供具有技术门槛的高性能芯片,正在该赛道上发挥更大的价值。

不过,头部势力如高通在智能座舱芯片领域的绝对统治,和NVIDIA芯片在自动驾驶领域构建的庞大的算法生态壁垒,也在加速其他芯片企业之间的“内卷”。

对于传统Tier1来说,软件定义汽车促使主机厂寻求主导权,开始由自己定义座舱方案;同时,域架构融合产品的加速量产上车,中央集中式架构的演进,这些都对其带来巨大影响,并将其推进转型的深水区。

目前,传统Tier1企业包括博世、安波福、德赛西威等,正在以垂直整合打造软硬件全栈的研发能力,完成从系统集成商到系统方案解决商的身份转变。

此外,随着座舱与智驾不断融合,终端车企也需进行自身策略调整。以往各司其职的智驾和座舱两大独立部门,需要根据自动驾驶不同级别,来确定由哪个部门主导开发舱驾融合方案,这就涉及到组织架构的重新调整。

有业内人士认为,在L2级别或以下阶段,座舱的功能和团队更加复杂,泊车团队相对较小,可以由座舱部门主导;L3级别及以上,自动驾驶方案复杂度直线上升,交给自动驾驶部门主导更为合适。

图源:哪吒汽车

小结

从分布式走向域集成,再到跨域融合,最终实现中央集成,在汽车电子电气架构的整个演进过程中,随着智能座舱和自动驾驶逐渐成为智能汽车的体验核心,座舱与智驾的更新迭代速度正逐渐依据汽车芯片的迭代速度,接近摩尔定律。

大算力芯片带来的舱驾融合热度,正不断发酵。目前,多家车企,如理想汽车、小鹏、埃安、路特斯等都在开发全新一代中央计算E/E架构核心技术与车型产品,以进一步提升整车的智能化集成水平。

行泊/舱泊一体之后,舱驾一体正作为迈出中央计算的第一步,待势乘时,以最快的速度奔赴“上车”。新战场开启,环环相扣的供应链上下游,皆在转型的深水区摸索着扎根自己的行业地位。

来源:盖世汽车

作者:余有言

本文地址:https://www.d1ev.com/news/qiye/203281

以上内容转载自盖世汽车,目的在于传播更多信息,如有侵仅请联系admin#d1ev.com(#替换成@)删除,转载内容并不代表第一电动网(www.d1ev.com)立场。

文中图片源自互联网,如有侵权请联系admin#d1ev.com(#替换成@)删除。