盖世汽车讯 6月11日,东芝电子器件与存储株式会社(东芝)和日本半导体株式会社(日本半导体)共同展示了一种改进方法,可提高高压横向双扩散MOS (Laterally Double Diffused MOS,LDMOS)的可靠性和性能。其中,LDMOS是在电机控制驱动程序等大量汽车应用中使用的模拟IC的核心组件。随着车辆电气化的不断发展,包括更广泛地部署高级驾驶辅助系统(ADAS),东芝和日本半导体将能够根据所需电压提供改进的LDMOS单元设计。

(图片来源:东芝)

众所周知,设计LDMOS时经常需要在可靠性和性能间进行取舍。横向寄生双极效应通常会降低人体模型(HBM)容差。而通过增加背栅比(backgate ratio)抑制横向寄生双极效应,HBM测量的静电放电(ESD)的容差会得到改善。然而,增加背栅比也会增加导通电阻,从而降低性能。截至目前,LDMOS设计人员仍然必须在HBM容差与更高的导通电阻之间取得平衡。

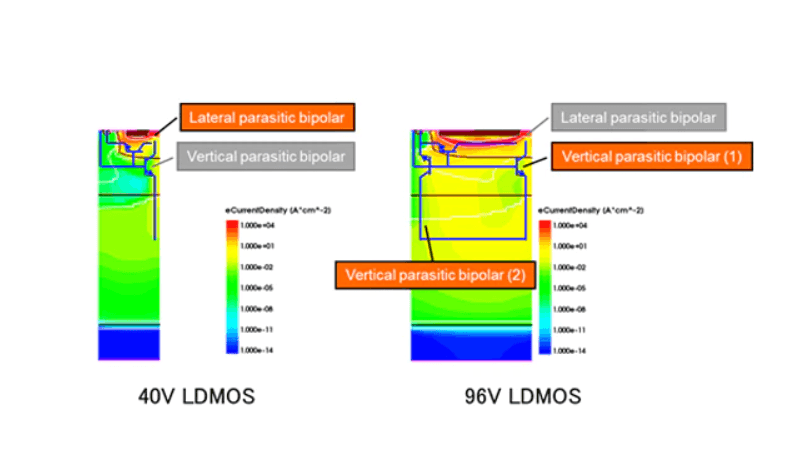

东芝和日本半导体对LDMOS中的HBM容差进行了评估,发现即使背栅比增加,在80V以上时容差也没有增加。他们发现这是因为在2D TCAD模拟中,垂直寄生双极效应与横向寄生双极效应一起出现,使设计人员在设置HBM和背栅比参数时具有更大的自由度。

东芝公司开发出一种技术,可优化除了背栅比(背栅的总宽度与源和背栅的总宽度之比)之外的单元设计参数。而将该技术与此次的发现相结合,东芝和日本半导体提出一种改善HBM容差并抑制80V及更高LDMOS导通电阻的方法,从而使得LDMOS可具有HBM容差,且不依赖背栅比。该方法可应用于发动机、转向系统等其他汽车系统中,将有助于提高可靠性和功率效率。

东芝拥有适用于各种应用、各种电压的LDMOS广泛产品阵容,并且正在开发可集成嵌入式非易失性存储器(eNVM)和高压模拟IC的第五代工艺技术。东芝和日本半导体致力于半导体工艺研发,为低功耗和高可靠性做出贡献。

来源:盖世汽车

作者:刘丽婷

本文地址:https://www.d1ev.com/news/jishu/149107

以上内容转载自盖世汽车,目的在于传播更多信息,如有侵仅请联系admin#d1ev.com(#替换成@)删除,转载内容并不代表第一电动网(www.d1ev.com)立场。

文中图片源自互联网,如有侵权请联系admin#d1ev.com(#替换成@)删除。